BELVIN

CONTROL DATA 924 COMPUTER

## 924 INSTRUCTIONS

|       |                   |      | Page     |     |                           |      | Page     |

|-------|-------------------|------|----------|-----|---------------------------|------|----------|

| ADD   | Add               | 14   | 2-17     | QLS | Q Left Shift              | 06   | 2-27     |

| ADL   | Add Logical       | 45   | 2-24     | QRS | Q Right Shift             | 02   | 2-26     |

| AJP   | A Jump            | 22   | 2-36, 40 | QTI | Q to Index                | 27   | 2-16     |

| ALS   | A Left Shift      | 05   | 2-27     | RAD | Replace Add               | 70   | 2-29     |

| ARS   | A Right Shift     | 01   | 2-26     | RAO | Replace Add One           | 72   | 2-29     |

| ATI   | A to Index        | 26   | 2-16     | RSB | Replace Subtract          | 71   | 2-29     |

| CMA   | Complement A      | 52 1 | 2-25     | RSO | Replace Subtract One      | 73   | 2-29     |

| CMQ   | Complement Q      | 52 2 | 2-25     | SAL | Substitute Address        | 61   | 2-13     |

| DVI   | Divide            | 25   | 2-19     | SBL | Subtract Logical          | 46   | 2-24     |

| ENA   | Enter A           | 10   | 2-15     | SCA | Scale A                   | 34   | 2-28     |

| ENI   | Enter Index       | 50   | 2-16     | SCL | Selective Clear           | 41   | 2-23     |

| ENQ   | Enter Q           | 04   | 2-15     | SCM | Selective Complement      | 42   | 2-22     |

| EQS   | Equality Search   | 64   | 2-33     | SCQ | Scale AQ                  | 35   | 2-28     |

| EXF   | External Function | 74   | 3-3      | SIL | Store Index               | 57   | 2-13     |

| IJP   | Index Jump        | 55   | 2-38     | SKH | Skip High                 | 30   | 2-31     |

| INA   | Increase A        | 11   | 2-21     | SKL | Skip Low                  | 31   | 2-31     |

| INI   | Increase Index    | 51   | 2-21     | SLJ | Selective Jump            | 75   | 2-37, 4  |

| INQ - | Increase Q        | 56   | 2-21     | SLS | Selective Stop            | 76   | 2-37, 40 |

| ISK   | Index Skip        | 54   | 2-31     | SSH | Storage Shift             | 37   | 2-30     |

| LAC   | Load A Complement | 13   | 2-11     | SSK | Storage Skip              | 36   | 2-30     |

| LDA   | Load A            | 12   | 2-11     | SST | Selective Set             | 40   | 2-22     |

| LDL   | Load Logical      | 44   | 2-24     | SSU | Selective Substitute      | 43   | 2-24     |

| LDQ   | Load Q            | 16   | 2-11     | STA | Store A                   | 20   | 2-12     |

| LIL   | Load Index        | 53   | 2-13     | STL | Store Logical             | 47   | 2-24     |

| LLS   | AQ Left Shift     | 07   | 2-26     | STQ | Store Q                   | 21   | 2-12     |

| LQC   | Load Q Complement | 17   | 2-11     | SUB | Subtract                  | 15   | 2-17     |

| LRS   | AQ Right Shift    | 03   | 2-26     | TAL | Tally                     | 62   | 2-20     |

| MEQ   | Masked Equality   | 66   | 2-34     | THS | Threshold Search          | 65   | 2-33     |

| MTH   | Masked Threshold  | 67   | 2-34     | UJP | Unconditional Jump        | 32   | 2-37     |

| MUI   | Multiply          | 24   | 2-18     | URJ | Unconditional Return Jump | 33   | 2-41     |

| PTS   | Pattern Search    | 63   | 2-34     | XAQ | Interchange A and Q       | 52 0 | 2-12     |

| QJP   | O Jump            | 23   | 2-37, 40 | XEC | Execute                   | 60   | 2-41     |

BELVIN

# CONTROL DATA 924 COMPUTER

## CONTENTS

## Chapter 1. Description

| Physical Description                   | 1-1  |

|----------------------------------------|------|

| 924 Characteristics                    | 1-3  |

| Logical Description                    | 1-4  |

| Storage Section                        | 1-4  |

| Input-Output                           | 1-6  |

| Arithmetic Section                     | 1-6  |

| Control Section                        | 1-8  |

| Chapter 2. Description of Instructions |      |

| Word Format                            | 2-1  |

| Execution Address                      | 2-2  |

| Address Modification                   | 2-2  |

| Sequential Execution of Instructions   | 2-4  |

| Instructions                           | 2-5  |

| Instruction Execution Time             | 2-6  |

| Order of Instructions                  | 2-7  |

| Full-Word Transmission                 | 2-11 |

| Address Transmission                   | 2-13 |

| Full-Word Arithmetic                   | 2-17 |

| Address Arithmetic                     | 2-20 |

| Logical                                | 2-22 |

| Shifting                               | 2-26 |

| Replace                                | 2-29 |

| Storage Test                           | 2-30 |

| Skip                                   | 2-31 |

| Storage Search                         | 2-33 |

| Jumps and Stops                        | 2-36 |

| Normal                                 | 2-36 |

| Return                                 | 2-39 |

## Chapter 3. Input-Output

| Methods of Data Exchange                           | 3-1  |

|----------------------------------------------------|------|

| Buffer Channels                                    | 3-1  |

|                                                    | 3-1  |

| Initiation and Control of Data Exchange            |      |

| Console Input-Output Equipment                     | 3-9  |

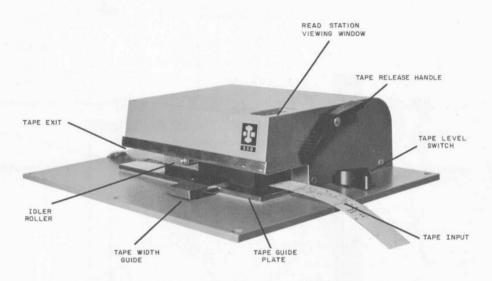

| Paper Tape Reader                                  | 3-9  |

| Paper Tape Punch                                   | 3-11 |

| Internal EXF Select Instructions                   | 3-13 |

| Buffer Mode Instructions                           | 3-13 |

| Channel Clear Instructions                         | 3-13 |

| Internal EXF Sense Instructions                    | 3-14 |

| Arithmetic Fault Instructions                      | 3-14 |

| Paper Tape Reader                                  | 3-14 |

| Paper Tape Punch                                   | 3-15 |

| Console EXF Sense Instructions                     | 3-16 |

| Paper Tape Reader                                  | 3-16 |

| Paper Tape Punch                                   | 3-16 |

| Chapter 4. Operation                               |      |

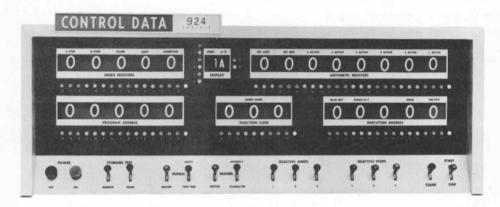

| Description of Indicators and Control Switches     | 4-1  |

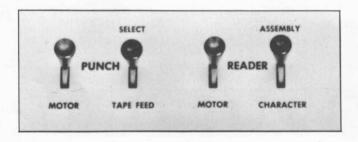

| Reader and Punch Controls                          | 4-6  |

| 1607 Controls and Indicators                       | 4-7  |

| Operation                                          | 4-8  |

| Starting Operation With Pre-Stored Load Program    | 4-8  |

| Starting Operation Without Pre-Stored Load Program | 4-11 |

| Shutting Down Equipment                            | 4-11 |

| Additional Procedures                              | 4-12 |

| Replacing Tape Roll at Punch                       | 4-12 |

| File Protection Ring                               | 4-13 |

| Emergency Procedures                               | 4-13 |

## Glossary

## Appendix Section

| I   | Number Systems                          | 1    |

|-----|-----------------------------------------|------|

| II  | Faults                                  | 12   |

| III | Table of Powers of 2                    | 14   |

| IV  | Octal-Decimal Integer Conversion Table  | 15   |

| V   | Octal-Decimal Fraction Conversion Table | 19   |

| VI  | EXF and Character Codes                 | 22   |

| VII | 924 Repertoire                          | 35   |

|     |                                         |      |

|     | FIGURES                                 |      |

|     | Chapter 1. Description                  |      |

| 1-1 | Main Cabinet Interior                   | 1-2  |

| 1-2 | 924 Input-Output System                 | 1-7  |

|     | Chapter 3. Input-Output                 |      |

| 3-1 | Instruction Searching                   | 3-6  |

| 3-2 | Seven Level Punched Paper Tape          | 3-10 |

|     | Chapter 4. Operation                    |      |

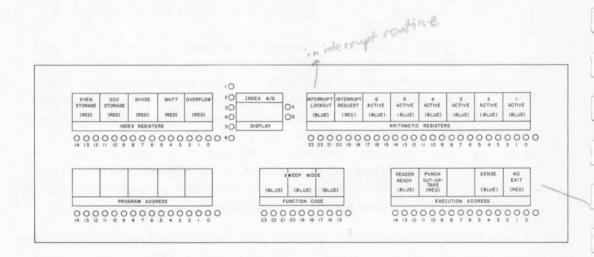

| 4-1 | Center Panel of Console                 | 4-1  |

| 4-2 | Console Display                         | 4-2  |

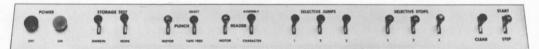

| 4-3 | Manual Controls                         | 4-5  |

| 4-4 | Reader and Punch Controls               | 4-6  |

| 4-5 | Paper Tape Reader                       | 4-9  |

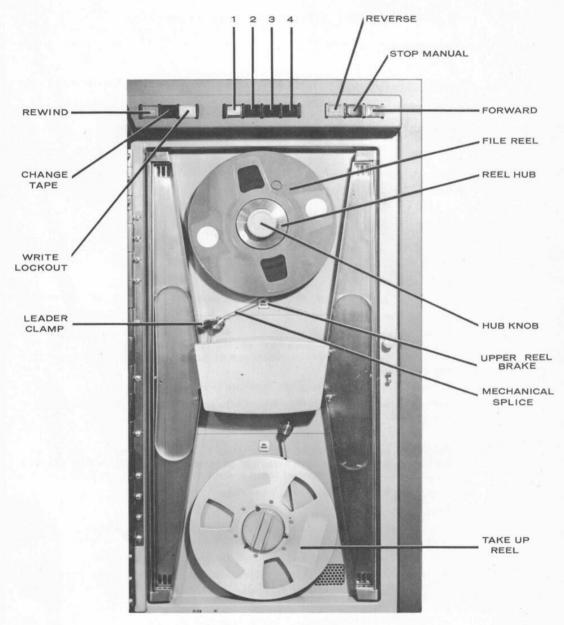

| 4-6 | Tape Unit                               | 4-10 |

| 4-7 | Paper Tape Punch                        | 4-12 |

| 4-8 | File Protection Ring                    | 1-12 |

## TABLES

|     | Chapter 1. Description                            |      |

|-----|---------------------------------------------------|------|

| -1  | Operational Registers of the Computer             | 1-5  |

| -2  | Arithmetic Properties of Registers                | 1-5  |

|     | Chapter 3. Input-Output                           |      |

| 3-1 | Typical Interrupt Routine                         | 3-8  |

|     | Chapter 4. Operation                              |      |

| 1-1 | Conditions Indicated by Console Background Lights | 4-3  |

| 1-2 | Main Computer Controls                            | 4-4  |

| 1-3 | Reader and Punch Controls                         | 4-6  |

| 1-4 | 1607 Controls and Indicators                      | 4-7  |

| 1-5 | Emergency Procedures                              | 4-13 |

Description

The Control Data 924 Computer is a general purpose digital computer designed to solve both business and scientific problems. The reliability of high-speed transistor amplifier circuits and the efficiency of parallel operations are combined in the 924 to produce exceedingly fast computation and transfer speeds. Greater speed, reliability, and efficiency coupled with modular construction and large storage capacity results in an extremely versatile and powerful computer having highly flexible systems applications.

## PHYSICAL DESCRIPTION

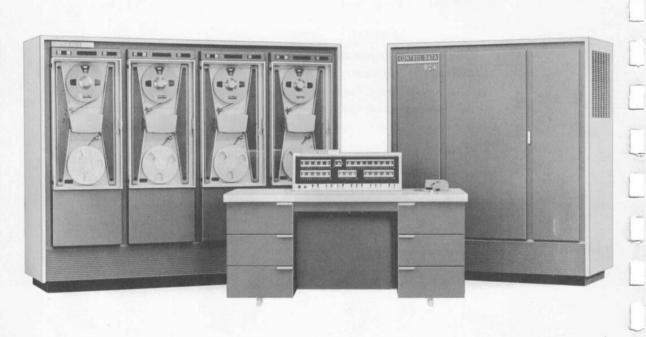

The basic 924 installation consists of two units; the console and main computer cabinet. An installation may also include, as optional equipment, any input-output devices capable of communication with the 160 and/or 1604 computer such as the 1607 Magnetic Tape System, the 1610 Punched Card Control Unit, the 1612 High Speed Line Printer and the 161 Typewriter.

The console contains the operator's display panel, controls, paper tape punch and paper tape reader.

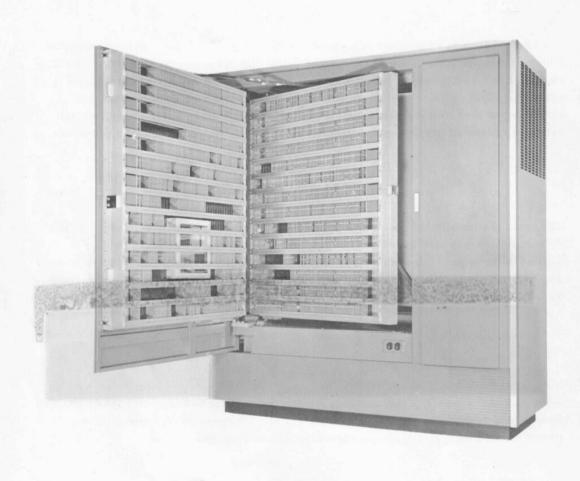

The main cabinet holds four chassis hinged for easy access (figure 1-1). Each chassis holds part of the core storage assembly and the pluggable printed circuit cards. Cabinet dimensions, to the nearest inch, are: Height 5 feet 8 inches, Depth 2 feet 2 inches, Length 5 feet 2 inches, and Weight approximately 1430 pounds.

Figure 1-1. Main Cabinet Interior

## 924 CHARACTERISTICS

Stored-program, general-purpose digital computer

Parallel mode

24-bit word, 1 instruction per word

Single-address logic

Operation code 6 bits

Index designator 3 bits

Execution address 15 bits

Six index registers

Indirect addressing

Magnetic core storage 8,192 24-bit words , 16 K, 32 K

Two independent 4096 word banks alternately phased <

5. 3 μsec effective cycle time (representative program)

6. 4 µsec total cycle time

Input-output

Three 48-bit buffer input channels, compatible with 1604 peripheral equipment, 12 lower-order bits compatible with 160 peripheral equipment.

Three 48-bit buffer output registers, compatible with 1604 peripheral equipment, 12 lower-order bits compatible with 160 peripheral equipment.

Program interrupt

Console, includes:

Photoelectric paper tape reader

Paper tape punch

Register contents displayed in octal

Flexible 64 instructions

Fixed point arithmetic

Logical and masking operations

Indexing

Input-output

Conditional and unconditional

Jumps and stops

Multiple precision capability

(accumulator and auxiliary register operate as a single double-length register)

Storage searching

Binary arithmetic Modulus  $2^{24}$ -1 (one's complement) Parallel addition in 1.2  $\mu$ sec without access

Real-time clock

Completely solid-state

Diode logic

Transistor amplifiers

Magnetic core storage

Small size

Less than 400 square feet of floor space required

Low power consumption

Optional features

Increase standard 8, 192 words of

magnetic core storage to 16, 384 or

32, 768 words

|   | Price | New Price | size<br>8K | Reat        |  |

|---|-------|-----------|------------|-------------|--|

| ş | 265 K | \$ 180K   | 8K         | 8 8 K/Monte |  |

|   | 300   | 2/6       | 16         | 7           |  |

|   | 370   | 288       | 32         | 11          |  |

## LOGICAL DESCRIPTION

The computer performs calculations and processes data in a parallel binary mode through the step-by-step execution of individual instructions which are stored internally along with the data.

Functionally, computer operation may be divided into four major sections. INPUT-OUTPUT provides communication between the computer and the external equipment; ARITHMETIC performs the arithmetic and logical operations required for executing instructions; STORAGE provides internal storage for data and instructions; and CONTROL coordinates and sequences all operations for executing an instruction by obtaining the instruction from storage and translating it into commands for the other sections.

The registers in the computer are identified by letters. The <u>operational</u> registers (table 1-1)usually hold the end result of an operation. Their contents are displayed on the console and may be manually changed by the operator. The arithmetic properties of these registers are detailed in table 1-2. The transient registers used in formulating the result are <u>secondary</u> registers. They are not displayed and cannot be manually changed.

#### STORAGE SECTION

The magnetic core storage section of the 924 Computer provides high-speed, random access storage for 8,192 words. It consists of two independent storage units each with a capacity of 4096 words. These units operate together during the execution of a stored program and thus are considered as one 8,192 word storage system.

A word is 24 bits in length and is used as a 24-bit instruction or a 24-bit operand (data word). The location of each word in storage is identified by an assigned number or address. When a word is taken (read) from or entered (written) into storage, a reference is made to the storage address which holds the word. All odd storage addresses are located in one storage unit; all even addresses in the other.

The cycle time, or time for a complete storage reference, is 6.4 microseconds. Since the storage cycles of the two sections overlap one another in the execution of a program, the average effective cycle time for random addresses is about 5.3 microseconds.

TABLE 1-1. OPERATIONAL REGISTERS OF THE COMPUTER

| Register                                    | Function                |

|---------------------------------------------|-------------------------|

| А                                           | Arithmetic              |

| Q                                           | Auxiliary<br>Arithmetic |

| B <sup>1</sup><br>through<br>B <sup>6</sup> | Index registers (six)   |

| P                                           | Program Address         |

| U                                           | Program Control         |

TABLE 1-2. ARITHMETIC PROPERTIES OF REGISTERS

| Register | No.<br>of stages | Modulus            | Complement<br>Notation* | Arithmetic  | Result   |

|----------|------------------|--------------------|-------------------------|-------------|----------|

| A        | 24               | 2 <sup>24</sup> -1 | one's                   | subtractive | signed** |

| Q        | 24               | 2 <sup>24</sup> -1 | one's                   |             | signed   |

| P        | 15               | 2 <sup>15</sup>    | two's                   | additive    | unsigned |

| U        | 15               | 215                | two's                   | subtractive | unsigned |

<sup>\*</sup> Refer to Appendix

<sup>\*\*</sup>The result of an arithmetic operation in A satisfies A  $\leq$  2  $^{23}$ -1 since A always is treated as a signed quantity. When the result in A is zero, it is always represented by 000...00 except when 111...11 is added to 111...11. In this case, the result is 111...11 (negative zero).

#### INPUT-OUTPUT

The input-output section of the computer handles the flow of information to and from the computer. Prior to executing a program, the data and instructions which comprise the program (input) are loaded into computer storage. After computation is completed, the results (output) are transmitted from storage to an external equipment. All information is transmitted in 24-bit words.

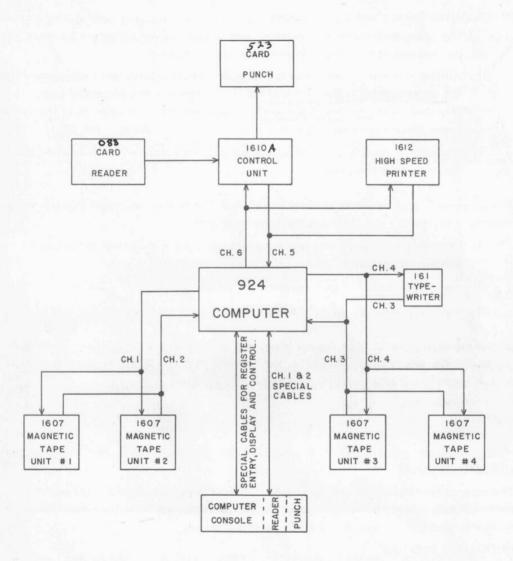

The computer communicates with external equipment through six independent buffer channels which provide for the normal exchange of data (figure 1-2).

| Input: | Channel 1 | Output: | Channel 2 |

|--------|-----------|---------|-----------|

|        | Channel 3 |         | Channel 4 |

|        | Channel 5 |         | Channel 6 |

The input and output buffer channels are paired, channels 1 and 2, channels 3 and 4, and channels 5 and 6. Every external equipment is connected to one of these pairs. It is possible to connect as many as five different equipments to any given pair of channels. All six buffer channels may be concurrently transmitting information. However, only one external equipment can use any one buffer channel at any given instant.

In the 924 computer, input-output operations are independent of the main computer program. When data is transmitted, the main computer program initiates an automatic cycle which buffers data to and from computer storage. The main computer program then continues while the actual buffering of data is carried out independently and automatically.

This process of asynchronous input-output operations will be termed a buffer. Buffer transmissions employ independent access to computer storage so that computation continues while the external equipment is loading or unloading information from computer storage. The rate of exchange is, in most cases, dictated by the external equipment.

#### ARITHMETIC SECTION

The arithmetic section of the 924 computer consists of two operational registers, A and Q, and several secondary registers.

The A register (accumulator) is the principal arithmetic register. Some of the more important functions of A are:

Sample

Figure 1-2. 924 Input-Output System

- 1) All arithmetic and logical operations use the A register in formulating a result.

The A register is the only register with provisions for adding its contents and the contents of a storage location or another register.

- 2) Shifting A may be shifted to the right or left separately or in conjunction with Q. Right shifting is open-ended; the lowest bits are discarded and sign extended. Left shifting is circular; the highest order bit appears in the lowest order stage after each shift; all other bits move one place to the left.

- 3) Control for conditional instructions A holds the word which conditions jump and search instructions.

The Q register is an auxiliary arithmetic register and is generally used in conjunction with the A register. The principal functions of Q are:

- 1) Providing temporary storage of contents of A while A is used for another arithmetic operation.

- 2) Forming a double-length register, AQ or QA.

- 3) Shifting to the right or left, separately or in conjunction with A.

Both A and Q may load, or be loaded from, any of the six index registers without the use of storage references. Similarly, the contents of A and Q may be interchanged to permit the use of Q as an auxiliary accumulator.

#### CONTROL SECTION

The control section directs the operations required to execute instructions and to exchange data with external equipment. It also establishes the timing relationships needed to perform the operations in the proper sequence.

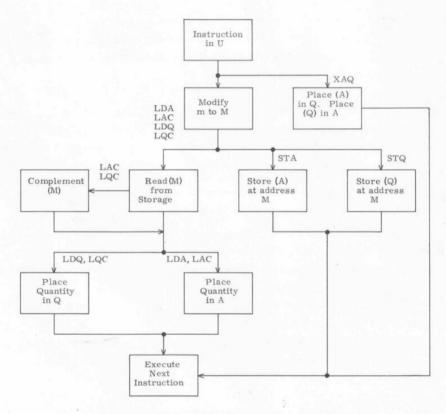

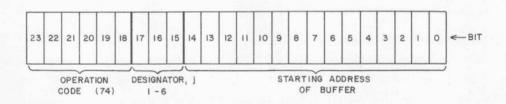

The control section acquires an instruction from storage, interprets it, and sends the necessary commands to other sections. The composition of a 924 instruction is shown below.

#### Instruction Format

| operation | index    | base execution                 |

|-----------|----------|--------------------------------|

| (6 bits)  | (3 bits) | m, y, or k or unused (15 bits) |

Each of the 64 instructions has an operation code which specifies the operation to be performed. This code is usually written as a 2 octal digit numeric code or as a mnemonic code (see appendix).

The index designator generally is used for address modification; it specifies one of the six index registers whose contents are to be added to the base execution address. The index designator may also condition jump and stop instructions, specify indirect addressing, or further distinguish between two unlike instructions having the same operation code.

The execution address may be used as an address of an operand, m; as an operand, y; or as a shift count, k.

The eight operational registers in the control section are P, U and  $B^1$  through  $B^6$ .

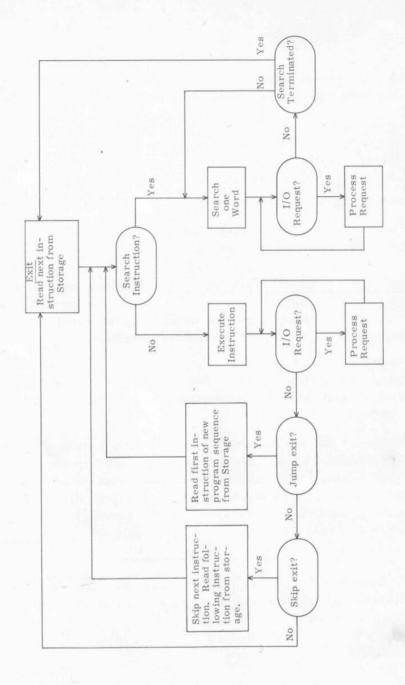

The program address counter (P) is a two's complement additive register. It provides program continuity by generating in sequence the storage addresses which contain the individual instructions. Usually at the completion of each instruction, the count in P is advanced by one to specify the address of the next instruction.

The program control register, U, holds an instruction while it is executed. After executing an instruction, an exit, jump exit or skip exit is performed. An exit advances the count in P by one and executes the next instruction specified by the contents of P. A jump exit executes the instruction at the storage location specified by the execution address of the jump instruction. The execution address is, in this case, entered into P and specifies the starting location of a new sequence of instructions. A skip exit advances the count in P by two, bypassing the next sequential instruction and executing the following one.

Each of the six index registers, B<sup>1</sup> through B<sup>6</sup>, provides storage for quantities which are used in a variety of ways, depending on the instruction. The B registers have no provisions for arithmetic operations. In the majority of instructions the B registers hold quantities to be added to the execution address. All address modifications are performed in A. For search instructions, the contents of a B register indicate the number of words to be search. This quantity is transmitted to U, and reduced one count for each word searched.

# Description of Instructions

## **WORD FORMAT**

A computer word consists of 24 bits and may be interpreted as a 24-bit instruction or data word. Each instruction is composed of three parts or codes: operation code, index designator, and execution address.

| bit<br>243              |                     |                      | bit<br>00 |

|-------------------------|---------------------|----------------------|-----------|

| Operation<br>(Function) | Index<br>Designator | Execution<br>Address |           |

| Code<br>f               | b                   | m, y, k              |           |

| 6                       | J 3 J               | 15                   |           |

| bits                    | bits                | bits                 |           |

| Code                            | Range                                  | Description.                                                                                                                                                                                                                                    |

|---------------------------------|----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operation f                     | 01 - 76 <sub>8</sub>                   | Specifies the operation to be performed. Codes 00, 52.3-52.6 and 77 are interpreted as faults which stop computer operation.                                                                                                                    |

| Execution<br>Address<br>m, y, k | 00000<br>through<br>77777 <sub>8</sub> | Used in one of three ways:  1) as a shift count k, or  2) as an operand address, m, r  3) as an operand, y.                                                                                                                                     |

| Index Designator b              |                                        | No address modification Relative address modification Specifies the index designator whose contents are to be added to the execution address. (Refer to jump and stop instructions for exceptions.) Indirect addressing (Refer to 22, 23, 74-76 |

#### Execution Address

The base execution address may be used as: (1) a shift count, k; (2) an operand, y; (3) an address of an operand, m, in storage. The execution address may also be modified or left unmodified depending on the index designator. If unmodified, the address is represented by the lower-case symbol k, y, or m; if the address is modified the symbols are capitalized. The following examples point out the relationship between the unmodified and modified execution address.

The modified shift count K is represented by:

1) K = k + (Bb) where: K = modified shift count k = unmodified shift count (execution address)

(Bb) = contents of index register b.

If the index designator = 0, then K = k.

The modified operand Y is represented by:

2)  $Y = y + (B^b)$  where: Y = modified operand y = unmodified operand (execution address) (B<sup>b</sup>) = contents of index register b.

If the index designator = 0, then Y = y.

The modified operand address M is represented by:

$M = m + (B^b)$  where: M = modified address of operand m = unmodified address of operand (execution address) (Bb) = contents of index register b.

If the index designator = 0, then M = m. Note that (3) is the only case in which the execution address is interpreted as an address of an operand.

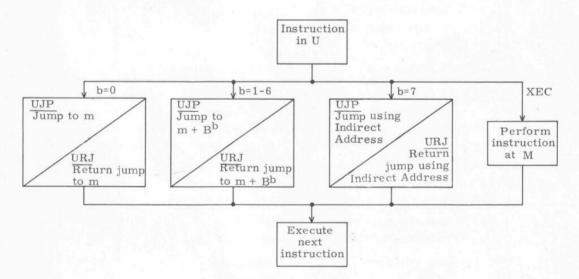

#### Address Modification

The three possible modes of address modification are identified by the index designators as follows:

1) b = 0No Address Modification. In this mode the execution address is interpreted without modification; nothing is added to or subtracted from it. (Direct addressing.)

- 2) b = 1-6 Relative Address Modification. In this mode the execution address is modified and is equal to the initial execution address plus the contents of the designated index register. One's complement arithmetic is used in determining the modified execution address.

- 3) b = 7 Indirect Addressing. In this mode a storage reference is made to the location designated by the execution address. The lower-order 18 bits of the 24-bit word are read from storage and interpreted as the b designator (3 bits) and execution address (15 bits) of the present instruction. The new index designator may refer to any one of the three modes.

## Examples:

1) No Address Modification LDA 0 address

This instruction is interpreted as load accumulator from the storage location

designated by the sum of the execution address and the contents of the specified index register, B<sup>b</sup>. Since b = 0, no index register is designated and m specifies the storage location whose contents are loaded into A.

- Relative Address Modification LDA 6 address (B<sup>6</sup>) = 00001<sub>8</sub>

In this example, the accumulator is loaded from the storage location designated by the execution address plus the contents of index register 6. Therefore, the contents of the storage location named by the execution address plus 00001<sub>8</sub> is loaded into the accumulator. M = m + (B<sup>b</sup>).

- 3) Indirect Addressing

Current Instruction =

$$LDA = 0.00100$$

(00100) =  $STA = 0.00018$

When the b designator of the current instruction is 7, the mode is indirect addressing. The lower 18 bits of the contents of the storage location designated by the execution address, 00100, are read from storage into the U register where they are interpreted as the index designator and execution address of the current instruction.

The index designator is inspected again and because it is not 0 or 7 the relative address mode exists. (Note that the new index designator could reference any one of the three modes of address modification.) The execution address, 00200, plus the contents of  $B^6$ , 00001 $_8$  specify the storage location whose contents will be loaded into the accumulator.  $M = 00200_8 + (00001_8) = 00201_8$

#### Sequential Execution of Instructions

Example:

The P register holds address 00300 (an even lowest bit indicates the address of the program step is in the even storage unit). The storage reference is initiated; the 24-bit word is read from address 00300 and entered into U. Computer operation is now dependent upon the interpretation of the 24-bit instruction in U.

The operation code, LDA, and the index designator, 0, are translated. The function of the instruction, LDA, is to load the A register with the contents of the designated storage location. Because the index designator is 0, the execution address is not modified. The translation of the operation code initiates the sequence of the commands which execute the instruction and the operand in address 00310 is loaded into A.

The contents of P are increased by one and the next instruction is read from storage address 00301. This instruction is now translated in U. The ADD instruction causes the quantity in storage location M to be added to the contents of the A register. Since the index designator is not 0 or 7, the contents of the index register are added to the execution address to form M.  $M = m + (B^b) = 00210_8 + 00101_8 = 00311_8$ . The contents of storage address 00311 are added to the contents of the A register completing the instruction. The contents of the P register are again increased by one and the instruction at address 00302 is read from storage and executed. This sequence is continued unless a jump or skip instruction is executed (see page 1-9).

## INSTRUCTIONS

The 64 computer instructions are described on the following pages, (EXF instructions are discussed in detail in chapter three). The title line contains the mnemonic code and format, name, and average execution time of the instruction. Abbreviations and symbols are defined as follows:

| А       | A register (accumulator)                                    |

|---------|-------------------------------------------------------------|

| An      | The binary digit in position n of the A register            |

| → ^ ^   | Transmit to                                                 |

| b       | Index designator                                            |

| $B^{b}$ | Designated index register                                   |

| Exit    | Proceed to next instruction                                 |

| j       | The condition designator for jump and stop instructions     |

| k       | Unmodified shift count                                      |

| K       | Modified shift count. $K = k + (B^b)$                       |

| m       | Unmodified operand address                                  |

| M       | Modified operand address. $M = m + (B^b)$                   |

| ( )     | Contents of a register or storage location                  |

| ( )'    | One's complement contents of a register or storage location |

| ( )f    | Final contents of a register or storage location            |

| ( )i    | Initial contents of a register or storage location          |

| Q       | Auxiliary arithmetic register                               |

| У       | Unmodified operand                                          |

| Y       | Modified operand. $Y = y + (B^b)$                           |

#### Instruction Execution Time

The time needed to execute an instruction varies from application to application because of the following factors.

If consecutive storage references are made to the same storage unit (even-even or odd-odd) the read access time from storage will be maximized.

If the base execution address is to be modified, the instruction execution time will be increased if consecutive instructions and operand addresses are used. There will be no increase in execution time if non-consecutive addresses are used for instructions and operand words.

If indirect addressing is specified, at least one additional reference will be needed to complete the instruction. (The new index designator may itself specify indirect addressing.)

If an input-output request exists, the request will, in most cases, be processed before the next instruction is executed. (Refer to chapter three.)

If a storage reference is made at the  $\underline{\underline{end}}$  of the preceding instruction, execution of the next instruction may be delayed.

The instruction execution times listed on the following pages were compiled by averaging the times for a long list of the same instructions. The list was arranged for typical values of the factors.

|      |                  |                     |       | be.       | CoBur            |

|------|------------------|---------------------|-------|-----------|------------------|

| Code | Mnemonic<br>Code | Name                |       | Timing*   | G                |

|      | FULL-WORD TR     | ANSMISSION          |       |           |                  |

| 12   | LDA              | LOAD A              |       | 9.9       | 1.63             |

| 13   | LAC              | LOAD A COMPLEMENT   |       | 9.9       | -13              |

| 16   | LDQ              | LOAD Q              |       | 9.9       |                  |

| 17   | LQC              | LOAD Q COMPLEMENT   |       | 9.9       |                  |

| 20   | STA              | STORE A             |       | 9.8       | 10.04            |

| 21   | STQ              | STORE Q             |       | 9.8       |                  |

| 520  | XAQ              | INTERCHANGE A AND Q |       | 6.2       |                  |

|      | ADDRESS TRAN     | ISMISSION           |       |           |                  |

| 53   | LIL              | LOAD INDEX          | 6.2   | 9.3       | 12,2             |

| .57  | SIL              | STORE INDEX         | 6.2   | 9.8       | 12. 2            |

| 61   | SAL              | SUBSTITUTE ADDRESS  | 6.0   | 9.8       | 12, 2 80 10.11   |

| 10   | ENA              | ENTER A             | Le la | 6.0       | 7,6              |

| 04   | ENQ              | ENTER Q             |       | 6.0       |                  |

| 26   | ATI              | A TO INDEX          |       | 7.0       |                  |

| 27   | QTI              | Q TO INDEX          |       | 6.0       |                  |

| 50   | ENI              | ENTER INDEX         |       | 6.20      |                  |

|      | FULL-WORD A      | RITHMETIC           |       |           |                  |

| 14   | ADD              | · ADD               | 6.0   | 9.9 12    | 3 92 108 12,     |

| 15   | SUB              | SUBTRACT            |       | 9.9       | "                |

| 24   | MUI              | MULTIPLY            | 12.2  | 27.9 + .8 | n* 10, y 19.9 18 |

| 25   | DVI              | DIVIDE              |       | 38.0      |                  |

|      | CO. A. T         | m * * * * * *       |       | 44.0      |                  |

<sup>\*</sup> Timing is average execution time in usec

<sup>\*</sup> n = Number of ones in multiplier

## ADDRESS ARITHMETIC

| 11  | INA      | INCREASE A           | 7.0         |

|-----|----------|----------------------|-------------|

| 51  | INI      | INCREASE INDEX       | 7.0         |

| 56  | INQ      | INCREASE Q           | 7.0         |

|     | LOGICAL  |                      |             |

| 40  | SST      | SELECTIVE SET        | 9.9         |

| 42  | SCM      | SELECTIVE COMPLEMENT | 9.9         |

| 41  | SCL      | SELECTIVE CLEAR      | 9.9         |

| 43  | SSU      | SELECTIVE SUBSTITUTE | 9.9         |

| 44  | LDL      | LOAD LOGICAL         | 9.9         |

| 45  | ADL      | ADD LOGICAL          | 9.9         |

| 46  | SBL      | SUBTRACT LOGICAL     | 9.9         |

| 47  | STL      | STORE LOGICAL        | 9.8         |

| 521 | CMA      | COMPLEMENT A         | 6.2         |

| 522 | CMQ      | COMPLEMENT Q         | 6.2         |

|     | SHIFTING |                      |             |

| 01  | ARS      | A RIGHT SHIFT        | 76.2 + .4s* |

| 02  | QRS      | Q RIGHT SHIFT        | 76.2 + .4s* |

| 03  | LRS      | AQ RIGHT SHIFT       | 6.2 + .4s*  |

| 07  | LLS      | AQ LEFT SHIFT        | 76.2 + .4s* |

| 06  | QLS      | Q LEFT SHIFT         | 6.2 + .4s*  |

| 05  | ALS      | A LEFT SHIFT         | 6.2 + .4s*  |

| 34  | SCA      | SCALE A              | 3.8+.4s*    |

| 35  | SCQ      | SCALE AQ             | 3.8 + .4s*  |

|     |          |                      |             |

<sup>\*</sup> s = Number of places shifted

| R  | EPLACE    |                      |              |

|----|-----------|----------------------|--------------|

| 70 | RAD       | REPLACE ADD          | 15.9         |

| 71 | RSB       | REPLACE SUBTRACT     | 15.9         |

| 72 | RAO       | REPLACE ADD ONE      | 15.9         |

| 73 | RSO       | REPLACE SUBTRACT ONE | 15.9         |

| S  | TORAGE SE | ARCH                 |              |

| 64 | EQS       | EQUALITY SEARCH      | 6.9 + 5.2r*  |

| 65 | THS       | THRESHOLD SEARCH     | 6 0 + 6 0 ** |

| 66 | MEQ       | MASKED EQUALITY      | 6.9 + 6.0r*  |

| 67 | MTH       | MASKED THRESHOLD     | 6.9 + 6.0r*  |

| 63 | PTS       | PATTERN SEARCH       | 6.9 + 6.0r*  |

| S  | TORAGE TE | ST                   |              |

| 36 | SSK       | STORAGE SKIP         | 9.2          |

| 37 | SSH       | STORAGE SHIFT        | 15.9         |

| SI | KIP       |                      |              |

| 54 | ISK       | INDEX SKIP           | €.0          |

| 30 | SKH       | SKIP HIGH            | 6.4          |

| 31 | SKL       | SKIP LOW             | 6.4          |

| JI | UMPS AND  | STOPS (Normal)       |              |

| 22 | AJP       | AJUMP                | 4.7          |

| 23 | QJP       | Q JUMP               | 4.7          |

| 75 | SLJ       | SELECTIVE JUMP       | 7.9          |

| 76 | SLS       | SELECTIVE STOP       | 7.9          |

| 32 | UJP       | UNCONDITIONAL JUMP   | 4.8          |

| 55 | IJP       | INDEX JUMP           | 7.0          |

r = Number of additional words searched

## JUMPS AND STOPS (Return)

|    | AJP | A JUMP                    | 7.7                               |

|----|-----|---------------------------|-----------------------------------|

|    | QJP | Q JUMP                    | 7.7                               |

|    | SLJ | SELECTIVE JUMP            | 7.9                               |

|    | SLS | SELECTIVE STOP            | 7.9                               |

| 33 | URJ | UNCONDITIONAL RETURN JUMP | 4.78                              |

| 60 | XEC | EXECUTE                   | 8.2 + x usec for instruction at M |

14 EXF EXTERNAL FUNCTION

# **FULL-WORD TRANSMISSION**

- 1) In Full-Word Transmission instructions, a 24-bit operand or data word is used in executing the instruction.

- 2) All modes of address modification apply to the full-word transmission instructions (except XAQ).

- 3) With the exception of XAQ, one storage reference is made during the execution of full-word transmission instructions. If indirect addressing is designated, at least two storage references are made. No storage reference is made during the execution of the XAQ instruction.

## LDA b m Load A

9.9 us

Replaces the contents of A with a 24-bit operand contained in storage location M. The contents of M remain unchanged.

#### LAC b m

Load A complement

9.9 us

Replaces the contents of A with the complement of a 24-bit operand contained in storage location M. The contents of M remain unchanged.

#### LDQ b m

Load Q

9.9 us

Replaces the contents of Q with a 24-bit operand contained in the storage location M. The contents of M remain unchanged.

#### LQC b m

Load Q Complement

9.9 us

Replaces the contents of Q with the complement of a 24-bit operand contained in storage location M. The contents of M remain unchanged.

#### STA b m

Store A

9.8 us

Replaces the contents of the designated storage location, M, with the contents of A. The initial contents of A remain unchanged.

Replaces the contents of the designated storage location, M, with the contents of Q. The initial contents of Q remain unchanged.

#### XAQ 0 m

Interchange A and Q\*

6.2 us

Places the contents of the A register into the Q register and at the same time places the contents of the Q register into the A register. The result of this instruction is that the contents of the A and Q registers are interchanged. The m portion of this instruction is not used.

LDA, LAC, LDQ, LQC, STA, XAQ, and STQ

<sup>\*</sup> If the index designator does not have the indicated value, the instruction will  $\underline{\text{not}}$  be executed.

# ADDRESS TRANSMISSION

- In the Address Transmission instructions, only the address portion (the lower 15 bits) of the word is used.

- 2) One storage reference is made during LIL, SIL, and SAL instructions. If indirect addressing is designated, at least two storage references are required. If indirect addressing is designated in the ENI instruction, one storage reference is required. No storage references are made for the remaining instructions.

- Address modification applies to the SAL, ENQ and ENA instructions only.

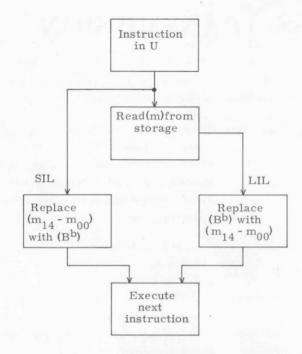

#### LIL b m Load Index

9.3 us

Replaces the contents of the designated index register with the address portion of storage location m. If b=0 this instruction becomes a pass (do nothing) instruction. Initial contents of m remain unchanged.

#### SIL b m

Store Index

9.8 us

Replaces the address portion of storage location m with the contents of the designated index register. The remaining bits of the word in storage remain unchanged. If b = 0, the address portion of m is set to all 1's. Initial contents of  $B^b$  remain unchanged; initial contents of m are changed.

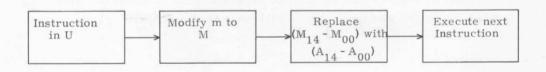

#### SAL b m

Substitute Address

9.8 us

Replaces the address portion of M with the lower order 15 bits of A. Remaining bits of M are not modified and the initial contents of A are unchanged.

LIL and SIL

SAL

The 15-bit operand, Y, is entered into the A register and its highest order bit (sign bit) is extended in the remaining 9 bits. The largest positive 15-bit operand that can be entered into A is  $37777_8$  ( $2^{14}$ -1) and the "0" sign bit will be duplicated in each of the upper 9 bits. Negative zero will be formed in A if:

- 1)  $(B^b) = 77777_8$  and  $y = 77777_8$  or

- 2) b = 0 and  $y = 77777_8$ .

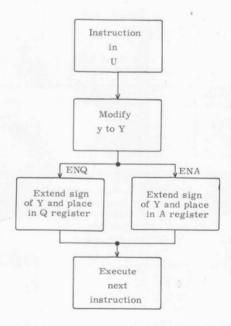

## ENQ by

Enter Q

7.0 us

The 15-bit operand, Y, is entered into Q and its highest order bit (sign bit) is extended in the remaining 9 bits. The largest positive 15-bit operand that can be entered into Q is  $37777_8$  ( $2^{14}$ -1) and its "0" sign bit will be duplicated in each of the upper 9 bits. Negative zero will be formed in Q if:

- 1)  $(B^b) = 77777_8$  and  $y = 77777_8$  or

- 2) b = 0 and  $y = 77777_8$ .

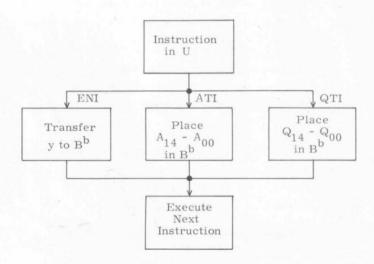

ENA and ENQ

This instruction transmits the lower order 15 bits of the A register to the index register specified by the index designator. The address portion of the instruction, m, is not used in this instruction. The contents of the A register are unchanged by this instruction.

## QTI b m Q to Index

7.0 us

This instruction transmits the lower order 15 bits of the Q register to the index register specified by the index designator. The address portion of the instruction, m, is not used in this instruction. The contents of the Q register are unchanged as a result of the instruction.

#### ENI by

Enter Index

6.2 us

Replaces  $(B^b)$  with the operand y. If b = 0, this instruction becomes a pass or do nothing instruction.

ATI, QTI, and ENI

# FULL-WORD ARITHMETIC

- In Full-Word Arithmetic instructions, a 24-bit operand is used in executing each instruction. The TAL instruction is unique in this category in that an operand, as such, is not used. The TAL instruction examines a 24-bit quantity in the A register.

- All modes of address modification apply to these instructions except TAL.

- One storage reference is made for each instruction except 3) TAL unless indirect addressing is designated. In this case, at least two references are made.

- If the capacity of the A register  $\pm$  (2<sup>23</sup>-1) is exceeded during 4) the execution of the instructions an arithmetic overflow fault is produced. When executing the DVI instruction, if the result exceeds the capacity of the A register ± (2<sup>23</sup>-1) a divide fault is produced. (Refer to appendix.)

### ADD b m

Add

9.9 118

Adds a 24-bit operand obtained from storage location M to (A). A negative zero may be produced by this instruction if (A) and (M) are initially negative zero. The contents of storage address M remain unchanged.

### SUB b m

Subtract

9.9 us

Obtains a 24-bit operand from storage location M and subtracts it from the initial contents of A. A negative zero will be produced if the initial contents of A are negative zero and that of storage location M are positive zero. The contents of address M remain unchanged.

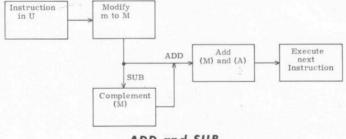

ADD and SUB

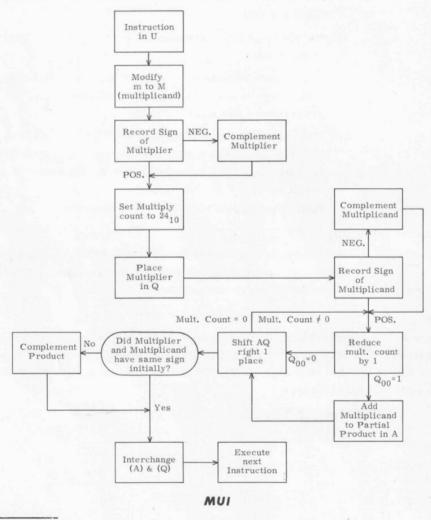

Forms a 48-bit product from two 24-bit operands. The multiplier must be loaded into A prior to execution of the instruction. The execution address specifies the storage location of the multiplicand. The product is contained in QA as a 48-bit quantity. The operands are considered as integers and therefore the binary point is assumed to be at the lower-order (right hand) end of the A register.

<sup>\*</sup> n = Number of ones in multiplier

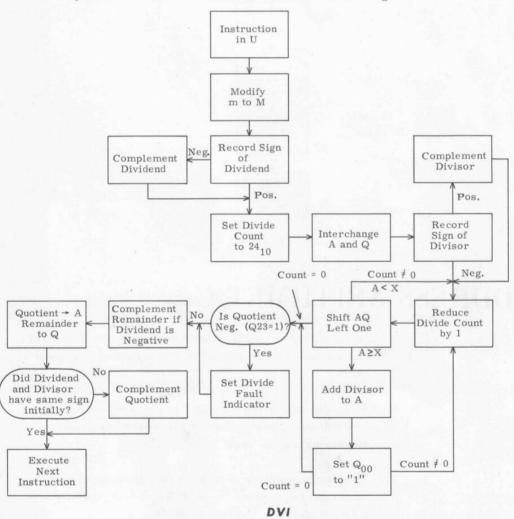

Divides a 48-bit integer dividend by a 24-bit integer divisor. The 48-bit dividend must be formed in the QA register prior to executing the instruction. If a 24-bit dividend is loaded into A, the sign of the dividend in A must be extended throughout Q. The 24-bit divisor is read from the storage location specified by the execution address. The quotient is formed in A and the remainder is left in Q at the end of the operation. Dividend and remainder have the same sign.

This instruction counts the number of ones in the A register and stores the count in the index register specified by the designator b; the contents of the A register remain unchanged. The m portion of the instruction is not used.

TALLY

# ADDRESS ARITHMETIC

- In the Address Arithmetic instructions, only the lower 15bits (or the address portion) of the operand or data word are used.

- All modes of address modification apply to the INA and INQ instructions. In executing the INI instruction, indirect addressing may be used.

- No storage reference is made during these instructions unless indirect addressing is designated. In this case, at least one storage reference is made.

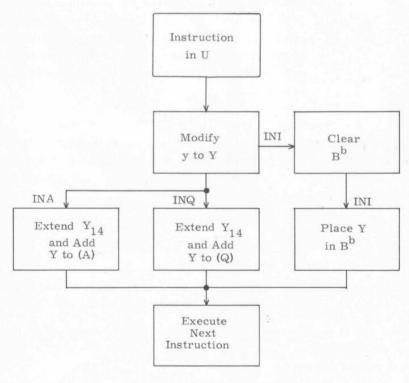

### INAby

Increase A

7.0 us

Adds Y to A. The 15-bit operand Y with its highest order bit is extended in the remaining 9 bits and added to A. Y is thus considered a 15-bit signed operand, with sign extended.

INI b y Increase Index 7.0 us

Increases (B<sup>b</sup>) by the operand y. If the b designator is zero, this instruction becomes a pass or do nothing instruction.

### INQ by

Increase Q

7.0 us

Adds Y to Q. The 15-bit operand Y, with its highest order bit extended in the remaining 9 bits, is added to Q. Y is thus considered as a 15-bit signed operand, with sign extended.

INA, INI, and INQ

### LOGICAL

- All modes of address modification apply to these instructions except CMA and CMQ.

- 2) The LDL, ADL, SBL and STL instructions achieve their result by forming a logical product. A logical product is a bit by bit multiplication of two binary numbers.

$$0 \times 0 = 0$$

$1 \times 0 = 0$   $0 \times 1 = 0$   $1 \times 1 = 1$

3) A logical product is used, in many cases, to select specific portions of an operand for entry into another operation.

For example, if only a specific portion of an operand in storage is to be added to (A), as the operand passes through the exchange register (X, a secondary register) it is subjected to a mask comprised of a predetermined pattern of "0's" and "1's". Forming the logical product of (X) and the mask causes X to retain the original contents only in those stages which have corresponding "1's" in the mask. When only the selected bits remain in X, the instruction proceeds to conclusion.

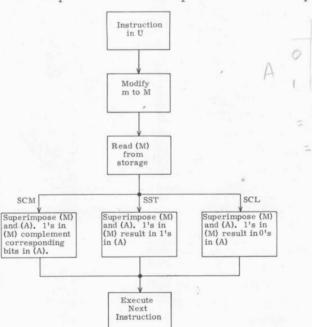

SST b m

Sets the individual bits of A to "1" where there are corresponding "1's" in the word at storage location M. "0" bits in the word at storage location M do not modify the corresponding bits in A. In a bit by bit comparison of (A) and (M) there are four possible combinations of bits.

1)

$$(A)_{i} = 1$$

2)  $(A)_{i} = 1$  3)  $(A)_{i} = 0$  4)  $(A)_{i} = 0$   $(M)_{i} = 1$   $(M)_{i} = 0$   $(M)_{i} = 1$   $(M)_{i} = 0$   $(M)_{i} = 1$   $(M)_{f} = 0$   $(M)_{f} = 1$   $(M)_{f} = 0$   $(M)_{f} = 0$

SCM b m

Selective Complement = Mod 2 Sum 9.9 us

Individual bits of A are complemented where there are corresponding "1's" in the word at storage location M. If the corresponding bits at M are "0's" the associated bits of A remain unchanged.

1)

$$(A)_{i} = 1$$

1)

$$(A)_{i} = 1$$

2)  $(A)_{i} = 1$   $(M)_{i} = 0$

3)

$$(A)_{i} = 0$$

$(M)_{i} = 1$

4)

$$(A)_{i} = 0$$

$(M)_{i} = 0$

$$(M)_i = 1$$

$$(A)_{f} = 1$$

$$(A)_f = 1$$

$$(A)_{f} = 0$$

$$(A)_{f} = 0$$

$$(M)_{f} = 1$$

$$(M)_{f} = 0$$

$$(M)_{\mathbf{f}}^{\mathbf{I}} = 1$$

$$(M)_{f} = 0$$

### SCL b m

Selective Clear

9.9 us

Clears individual bits of A where there are corresponding "1's" in the word at storage location M. If the corresponding bits at M are "0's" the associated bits of A remain unchanged.

In a bit by bit comparison of (A) and (M) there are four possible combinations of bits.

1)

$$(A)_{i} = 1$$

$(M)_{i} = 1$

2)

$$(A)_{i} = 1$$

3)

$$(A)_i = 0$$

4)

$$(A)_{i} = 0$$

$(M)_{i} = 0$

$$(A)_{f} = 0$$

$$(M)_{i} = 0$$

$(A)_{f} = 1$

$$(M)_{i} = 1$$

$(A)_{f} = 0$

$$(A)_{\mathbf{f}} = 0$$

$$(M)_{f} = 1$$

$$(M)_{f} = 0$$

$$(M)_{f} = 1$$

SCM, SST, and SCL

(Q. M + 8'A) - A

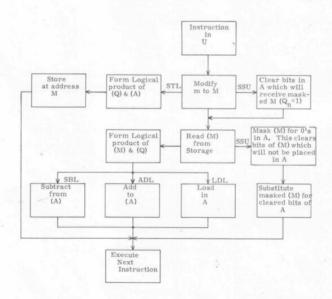

SSU b m

Selective Substitute

9.9 us

Substitutes selected portions of an operand at storage address M into the A register where there are corresponding "1's" in the Q register (mask). The portions of A not masked by "1's" in Q are left unmodified.

LDL b m

Load Logical

(0.M-A

Loads A with the logical product of Q and the designated storage location, M.

ADL b m

Add Logical

(Q M + A) - A 9.9 us

Adds to A the logical product of Q and the quantity in location M. Once the logical product is formed addition follows normal rules.

SBL b m

Subtracts from A the logical product of the Q register and the quantity in storage location M. When the logical product is formed, the subtraction proceeds in the normal manner.

STL b m

Store Logical

9.8 us

Replaces the bits in location M with the logical product of Q and A registers. Neither (A) or (Q) are modified.

ADL, LDL, SBL, SSU, and STL

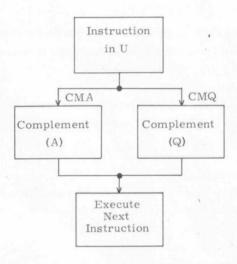

### CMA 1 m

Complement A\*

6.2 us

This instruction complements the contents of the A register. The address portion of this instruction, m, is not used.

### CMQ 2 m

Complement Q\*

6.2 us

This instruction complements the contents of the Q register. The address portion of this instruction, m, is not used.

CMA and CMQ

<sup>\*</sup> If the index designator does not have the indicated value, the instruction will  $\underline{\text{not}}$  be executed.

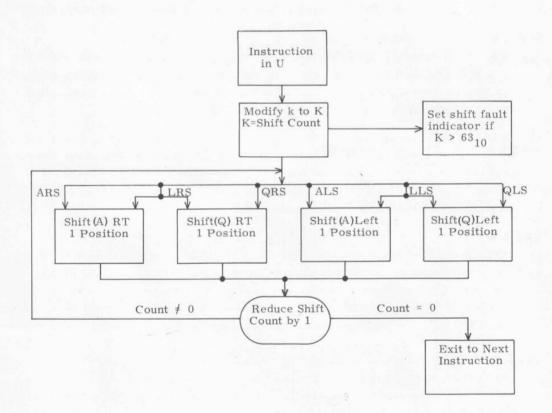

# **SHIFTING**

- All modes of address modification apply to all these instructions, except SCA and SCQ.

- 2) If the modified shift count, K, is greater than  $63_{10}$ , a fault indicator is set. Regardless of the magnitude of count, however, the required number of shifts is executed. (K is reduced by one count for each shift executed and when K = 0, shifting stops.)

- 3) Shifting will be completed before an input, output or interrupt request will be processed. (See chapter three.)

### ARS b k A Right Shift

6.2 + .4s\*

Shifts contents of A to the right K places. The sign is extended and the lower bits are discarded. The largest practical shift count is  $23_{10}$  since the register is now an extension of the sign bit.

### QRS b k Q

Q Right Shift

6.2 + .4s\*

Shifts contents of Q to the right K places. The sign is extended and the lower bits are discarded. The largest practical shift count is  $23_{10}$  since the register is now an extension of the sign bit.

### LRSbk

Long Right Shift

6.2 + .4s\*

Shifts contents of AQ to the right K places as one 48-bit register. The A register is considered as the leftmost 24 bits and the Q register as the rightmost 24 bits. The sign of A is extended. The lower order bits of A replace the higher order bits of Q and the lower order bits of Q are discarded. The largest practical shift count is  $47_{10}$  since AQ is now an extension of the sign of A.

### LLS b k

Long Left Shift

6.2 + .4s\*

Shifts contents of AQ to the left K places, left circular, as one 48-bit register. The higher order bits of A replace the lower order bits of Q and the higher order bits of Q replace the lower order bits of A. The largest practical shift count  $48_{10}$  returns AQ to its original state.

<sup>\*</sup> s = Number of positions shifted

Shifts contents of Q to the left K places, left circular. The higher order bits of Q replace the lower order bits. The largest practical shift count  $24_{10}$  returns the register to its original state.

### ALS bk

A Left Shift

6.2 + .4s\*

Shifts contents of A to the left K places, left circular. The higher order bits of A replace the lower order bits. The largest practical shift count  $24_{10}$  returns the register to its original state.

Shift Instructions

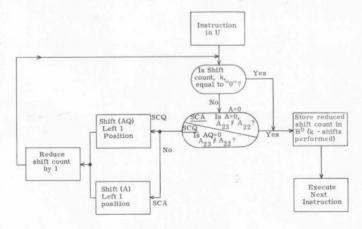

In the SCA and SCQ instructions:

- Address modification does not apply. Rather, the index register is used to preserve the scale factor.

- 2) If b = 0, scaling is executed but the scale factor is lost.

- 3) If b = 7, indirect addressing is used and at least one storage reference is made.

- 4) If the (A)i is already scaled or equal to positive or negative zero,  $k \rightarrow B^b$  and scaling is not executed.

- 5) If the execution address is initially equal to 0, Bb is cleared.

- 6) The shift fault indicator is not affected by these instructions.

### SCAbk

Scale A

3.8 + .4s\*

Shifts A left circularly until the most significant digit is to the right of the sign bit or until k=0. Shift count k is reduced by one for each shift and terminates when k=0 or the most significant digit is to the right of the sign bit. Upon termination the count (scale factor) is entered in the designated index register.

### SCQ bk

Scale AQ

3.8 + .45\*

Shifts AQ left circularly until the most significant digit is to the right of the sign bit. Shift count k is reduced by one for each shift. Operation terminates when k=0 or the most significant digit is to the right of the sign bit. Upon termination the count (scale factor) is entered in the designated index register.

SCA and SCQ

<sup>\*</sup> s = Number of positions shifted

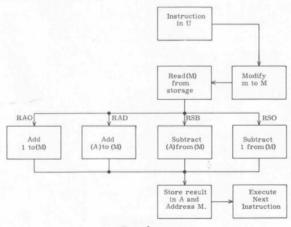

## REPLACE

- 1) All modes of address modification apply to these instructions.

- 2) During the execution of the replace instructions, two storage references are made. If indirect addressing is designated, at least three references are made.

- 3) If the capacity of the A register ± (2<sup>23</sup>-1) is exceeded during the execution of the following instructions, an arithmetic overflow fault is produced. (Refer to appendix.)

RADbm

Replace Add

15.9 us

Obtains a 24-bit operand from storage location M and adds it to the initial contents of A. The sum is left in A and is also transmitted to location M.

RSB b m

Replace Subtract

15.9 us

Subtracts (A) from (M) and places the result in both the A register and location M.

RAO b m

Replace Add One

15.9 us

Replaces the operand in storage location M with its original value plus one. The result is also placed in A.

RSO b m

Replace Subtract One

15.9 us

Replaces the operand in storage location M with its original contents minus one. The difference is also left in A,

Replace

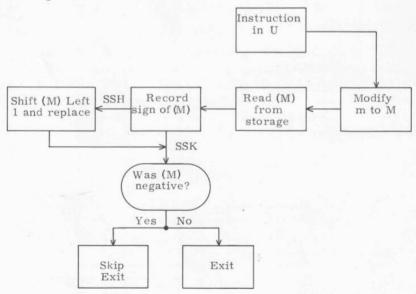

## STORAGE TEST

- All modes of address modification may be used in these instructions.

- 2) At least one storage reference is made unless indirect addressing is designated in which case at least two storage references are made.

### SSK b m

Storage Skip

9.2 us

Senses the sign bit of the operand in storage location M. If the sign is negative, a skip exit is taken. If the sign is positive, an exit is taken. The contents of the operational registers are left unmodified.

### SSH b m

Storage Shift

15.9 us

Senses the sign bit of the quantity in storage location M. If the sign bit is negative a skip exit is taken, and if the quantity is positive an exit is taken. In either case the quantity is shifted left circularly one bit before the exit. The contents of the operational registers are left unmodified.

SSH and SSK

### SKIP

- Indirect addressing is the only mode of address modification recognized by these instructions.

- No storage reference is made unless indirect addressing is specified in which case at least one reference will be made.

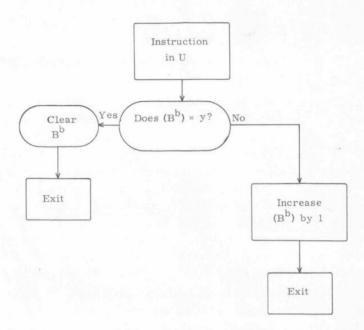

ISK b y Index Skip 7.0 us

Compares (B<sup>b</sup>) with y. If the two quantities are equal, B<sup>b</sup> is cleared and a skip exit is performed. If the quantities are unequal, (B<sup>b</sup>) is increased one count in the U register and an exit is performed. Counting is performed in a two's complement subtractive counter, thus, it is possible to count through negative zero and positive zero.

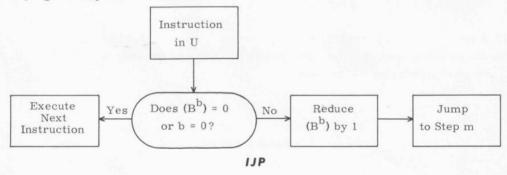

SKH b y Skip High 6.4 us

Compares the quantity in the designated index register with the operand, y. If the quantity in the index register is greater than or equal to the quantity y, an exit is performed. If the quantity in the index register is less than the quantity y, a skip exit is performed. The contents of the index register are unchanged by this instruction.

SKL b y Skip Low 6.4 us

Compares the quantity in the designated index register with the operand, y. If the quantity in the index register is less than the quantity y, an exit is performed. If the quantity is greater than or equal to y, a skip exit is performed. The contents of the index register are unchanged by this instruction.

ISK

SKH and SKL

# STORAGE SEARCH

- 1) If b = 0 in the following instructions only the word at storage location m will be searched.

- 2) If b = 7, indirect addressing is used to obtain the execution address and b designator.

- 3) If  $(B^b) = 0$ , no search is made.

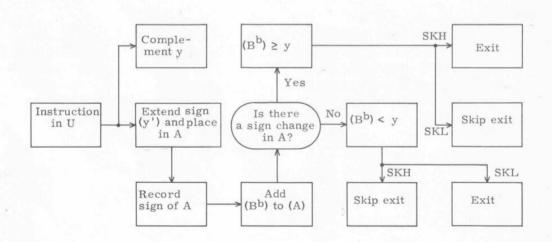

### EQS b m

Equality Search

6.9 + 5.2r\*

Searches a list of operands to find one that is equal to (A). The number of items to be searched is specified by  $(B^b)$ . These items are in sequential addresses beginning at location m. The search begins with the last address,  $m + (B^b) - 1$ .  $(B^b)$  is reduced one count for each word that is searched until an operand is found that equals (A) or until  $(B^b)$  equals zero. If the search is terminated by finding an operand that equals (A), a skip exit is made. The address of the operand satisfying this condition is given by the sum of m and the final contents of  $B^b$ . If no operand is found that equals (A), an exit is taken. Positive zero and minus zero are recognized as the same quantity.

### THS b m

Threshold Search

6.9 + 6.0r\*

Searches a list of operands to find one that is greater than (A). The number of items to be searched is specified by  $(B^b)$ . These items are located in sequential addresses beginning at location m. The search begins with the last address,  $m+B^b-1$ . The content of the index register is reduced by one for each operand examined. The search continues until an operand is reached that is greater than (A) or until  $(B^b)$  is reduced to zero. If the search is terminated by finding an operand greater than the value in A, a skip exit is performed. The address of the operand satisfying the condition is given by the sum of m and the final contents of  $B^b$ . If no operand in the list is greater than the value in A, an exit is performed. In the comparison made here positive zero is considered as greater than minus zero.

<sup>\*</sup> r = Number of additional words searched

### MEQ b m

Masked Equality

6.9 + 6.0r\*

Searches a list of operands to find one such that the logical product of (Q) and (M) is equal to (A). This instruction, except for the mask in Q, operates in the same manner as an equality search.

### MTH b m

Masked Threshold

6.9+6.0r\*

Searches a list of operands to find one such that the logical product of (Q) and (M) is greater than (A). Except for the mask in Q, this instruction operates in the same manner as the threshold search.

### PTS b m

Pattern Search

6.9 + 6.0r\*

Searches a list of operands to find one such that the inclusive or of (A) and (M) is equal to (A). These items are in sequential addresses beginning at the location specified by m. The search begins with the last address, m + Bb - 1. (Bb) is reduced one count for each word that is searched until an operand is found that satisfies the criteria or until (Bb) equals zero. If the search is terminated by finding an operand which satisfies the condition, a skip exit is performed. The address of the operand satisfying the inclusive or condition is given by the sum of m and the final contents of B<sup>b</sup>. If no operand in the list is found such that the inclusive or of (A) and (M) = (A), an exit is performed.

On a bit-by-bit basis, three combinations of the initial values of A and M meet the search criterion; one combination does not. The combinations are:

$$A_i = 0$$

$A_i = 1$   $M_i = 0$

Search criterion met

Search criterion not met

A ± M = A => A includes M A O M ~ M C A

<sup>\*</sup> r = Number of additional words searched

Search

# JUMPS AND STOPS

1) Address modification is used in the UJP instruction.

### NORMAL

2) If indirect addressing is designated for the IJP or UJP instruction, at least one storage reference is required.

A jump instruction causes a current program sequence to terminate and initiates a new sequence at a different location in storage. The Program Address Register, P, provides the continuity between program steps and always contains the storage location of the current program step.

When a jump instruction occurs, P is cleared and a new address is entered. In most jump instructions, the execution address, m, specifies the beginning address of the new program sequence. The word at address m is read from storage, placed in U and the first instruction of the new sequence is executed.

Some of the jump instructions are conditional upon a register containing a specific value or upon the position of an operator's jump or stop key on the console. If the criterion is satisfied, the jump is made to location m. If it is not satisfied, the program proceeds in its regular sequence to the next instruction.

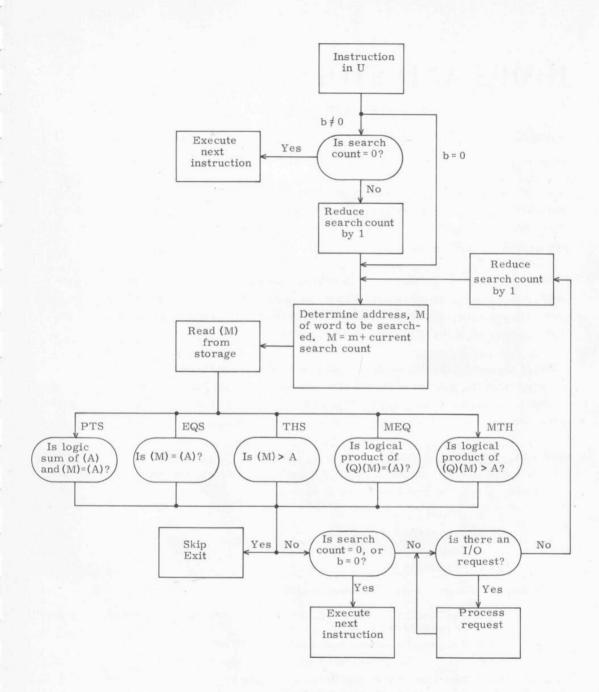

### AJP i m

A Jump

7.7 us

Jumps to m if the conditions of the A register specified by the jump designator j exist. If not, the next instruction is executed.

j = 0 jump if (A) = 0

j = 1 jump if (A)  $\neq 0$

j = 2 jump if (A) = +

j = 3 jump if (A) = -

When (A) is negative zero the interpretation is:

- j = 0 The jump is executed because, in this case, negative zero is recognized as positive zero.

- j = 1 The jump is not executed when (A) = +0 or 0.

- j = 2 The jump is not executed because the sign bit is a "1".

- j = 3 The jump is executed because the sign bit is a "1".

QJP i m

Q Jump

7.7 us

Jumps to m if the condition of the Q register specified by the jump designator, j, exists. If not, the next instruction is executed.

j = 0 jump if (Q) = 0

j = 1 jump if (Q)  $\neq 0$

i = 2 jump if (Q) = +

j = 3 jump if (Q) = -

When (Q) is negative zero the AJP interpretation applies.

SLJ j m

Selective Jump

7.9 us

Jumps to m if the condition of the jump keys specified by j exists. If not, the next instruction is executed.

j = 0 Jump unconditionally. (Does not reference jump key setting.)

j = 1 Jump if jump key 1 is set.

j = 2 Jump if jump key 2 is set.

j = 3 Jump if jump key 3 is set.

SLS j m

Selective Stop

7.9 us

Stops at present step in the sequence if the condition of the stop key specified by j exists. If the stop condition exists, the stop is executed, and the jump is executed unconditionally when the Run-Step Key is moved to the run or step position. If the stop condition is not satisfied, the jump is executed unconditionally.

j = 0 Stop unconditionally. (Does not reference stop key setting.)

j = 1 Stop if stop key 1 is set.

j = 2 Stop if stop key 2 is set.

j = 3 Stop if stop key 3 is set.

UJP b m

Unconditional Jump

4.8 us

Jumps unconditionally to M.  $M = m + (B^b)$ . If b = 0, the jump is to m. If b = 7, indirect addressing will be used.

AJP, QJP, SJP, and SLS

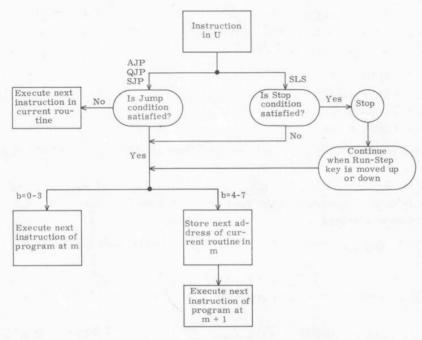

IJP b m Index Jump 7.0 us

Examines (B<sup>b</sup>). If this quantity is not zero, the quantity is reduced one count and a jump is executed to program step m. The counting operation is performed in a two's complement subtractive counter but negative zero is not generated because LIP terminates at positive zero. (See appendix.) If (B<sup>b</sup>) is zero, the present program sequence is continued.

1) Address modification applies only to URJ and XEC.

### RETURN

2) One storage reference is made.

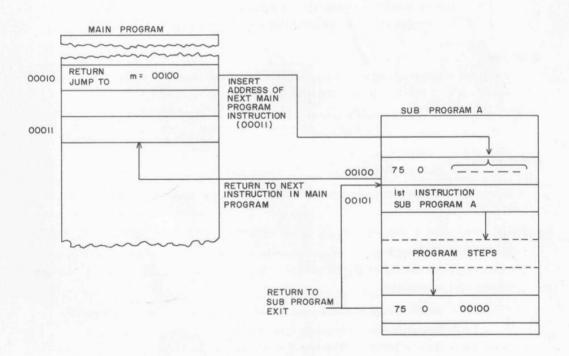

A return jump begins a new program sequence at the address specified by m+1, e.g., 00101. At the same time, the execution address of the first instruction in the new program sequence, 00100, is replaced with the address of the next program step in the main program (00011). The first instruction in a new program sequence is usually an unconditional jump which allows a return to the main program after completing the subprogram sequence.

Return Jump

### AJP i m

A Jump

7.7 us

Executes a return jump to storage location m if the condition of the A register specified by j exists. If not, the next instruction is executed.

- j = 4 Return jump if (A) = 0

- j = 5 Return jump if (A)  $\neq 0$

- j = 6 Return jump if (A) = +

- j = 7 Return jump if (A) = -

### When (A) is negative zero the interpretation is:

- j = 0 The return jump is executed because, in this case, negative zero is recognized as positive zero.

- j = 1 The return jump is not executed when (A) = + 0 or 0.

- j = 2 The return jump is not executed because the sign bit is a "1".

- j = 3 The return jump is executed because the sign bit is a "1".

### QJP i m

Q Jump

7.7 us

Executes a return jump to storage location m if the condition of the Q register specified by j exists. If not, the next instruction is executed.

- j = 4 Return jump if (Q) = 0

- j = 5 Return jump if (Q)  $\neq 0$

- j = 6 Return jump if (Q) = +

- j = 7 Return jump if (Q) = -

Note: If (Q) = negative zero, refer to the AJP instruction.

### SLJ i m

Selective Jump

7.9 us

Executes a return jump to storage location m on condition j where condition j represents the setting of the jump keys. If the condition is not satisfied, the next instruction is executed.

- j = 4 Return jump unconditionally. (Does not reference jump keys.)

- j = 5 Return jump if jump key 1 is set.

- j = 6 Return jump if jump key 2 is set.

- j = 7 Return jump if jump key 3 is set.

Note: The set position of a jump key is in the up position.

Stops on condition j and executes a return jump if the Run-Step key is moved in the run or step position. If the stop condition is not satisfied, the stop is not executed and the return jump is executed unconditionally.

- j = 4 Stop unconditionally. The return jump is executed when the Run-Step key is moved in either position.

- j = 5 Stop if stop key 1 is set. (Return jump.)

- j = 6 Stop if stop key 2 is set. (Return jump.)

- j = 7 Stop if stop key 3 is set. (Return jump.)

# URJ b m Unconditional Return Jump 4.8 us Return jumps unconditionally to M. $M = m + (B^b)$ . If b = 0, the return jump is to m. If b = 7, indirect addressing will be used

Jumps to M. After executing M, the main sequence is continued unless M performs a jump. In this case, a new program is initiated at the location specified by the jump and a return is not effected to the main sequence. This instruction is effectively an indirect instruction, or a subroutine of a single instruction.

UJP, URJ, and XEC

Input-Output

### METHODS OF DATA EXCHANGE

The computer communicates with external equipment via six buffer channels. These channels provide for the parallel transmission of binary words to and from computer storage.

### **BUFFER CHANNELS**

The six independent buffer channels are grouped in three pairs:

| Input: | Channel 1 | Output: | Channel 2 |

|--------|-----------|---------|-----------|

|        | Channel 3 |         | Channel 4 |

|        | Channel 5 |         | Channel 6 |

Every external equipment is connected to one of these pairs. All six buffer channels may be concurrently transmitting information. However, only one external equipment can use any one buffer channel at any given instant. The rate of data flow on the buffer channels is usually dependent on the operating speed of the external equipment.

### INITIATION AND CONTROL OF DATA EXCHANGE

The actual buffer (exchange) operation, although program initiated, proceeds under controls that are independent of the program. Information is buffered asynchronously with the execution of the program, thus, storage is permitted to serve its primary function of working with the arithmetic and control sections during the time a buffer is in progress.

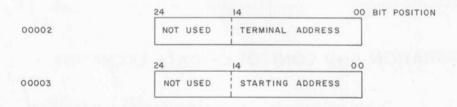

### Buffer Control Word

Information is buffered in blocks one word at a time. The current and terminal storage addresses of the block are located in adjacent storage locations called buffer control words. Each of the six buffer channels has two assigned storage addresses which hold the buffer control word for the current and terminal addresses of the block.

### Special Address

| 00000 | Initial start                        |

|-------|--------------------------------------|

| 00002 | Channel 1 control (terminal address) |

| 00003 | Channel 1 control (current address)  |

| 00004 | Channel 2 control (terminal address) |

| 00005 | Channel 2 control (current address)  |

| 00006 | Channel 3 control (terminal address) |

| 00007 | Channel 3 control (current address)  |

| 00010 | Channel 4 control (terminal address) |

| 00011 | Channel 4 control (current address)  |

| 00012 | Channel 5 control (terminal address) |

| 00013 | Channel 5 control (current address)  |

| 00014 | Channel 6 control (terminal address) |

| 00015 | Channel 6 control (current address)  |

|       |                                      |

#### Buffer Control Words

The terminal address is one greater than the last address to be used in the buffer. Prior to initiating a buffer operation, the terminating address must be entered into the even addressed control word. The starting address is automatically entered into the word when the buffer is initiated by an EXF instruction.

The execution address of the EXF instruction is used to designate the buffer starting address in storage. This address is automatically recorded in the lower 15 bits of the appropriate odd-number special storage location. The terminal address (plus one) of the block of data must have been previously recorded, by the program, in the lower 15-bit portion of the appropriate even-numbered special storage location prior to the execution of the external function instruction.

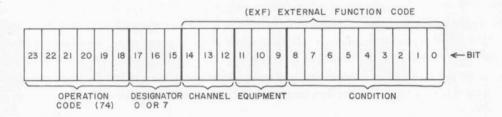

### External Function (EXF) Instructions

The EXF instructions initiate a buffer, sense for specified conditions, and select operations and equipment. EXF codes are listed at the end of the chapter.

16166

There are three kinds of external instructions:

| Select   | 74 0 XXXXX |  |

|----------|------------|--|

| Sense    | 74 7 XXXXX |  |

| Activate | 74 j XXXXX |  |

The composition of an external function instruction is shown below.

### Select and Sense

### Activate

The 74 0 (EXF Select) instructions select the external equipment which is to communicate with the computer and/or its mode of operation. The select instructions do not activate the buffer but, rather, establish initial operating conditions within the designated equipment so that information will be properly processed when the buffer is activated.

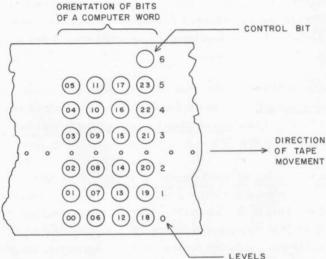

Three basic modes of communication can be selected by an EXF instruction: 1604 (48-bit), 160 (12-bit), and 24-bit. Selecting 1604 or 160 mode permits communication with any peripheral equipment.

No distinction is made between 24 and 48-bit transmissions on the control lines. However, when 24-bit mode is selected, a single storage word is read; two storage words are required for each 48-bit transmission.

When 160 mode is selected, the computer appears as a 160 to the peripheral equipments. The Status Request is accomplished by a one word output buffer which is a Select code because its sign bit is "1". If the sign bit is a "0", the output word is accepted as a word of information by the peripheral equipment. Only the lower 12 bits and the sign bit (bit 23) are significant during this mode. The lower 12 bits contain the Status Request code. The sign bit is a Function Ready signal to the peripheral equipment and indicates a select or Status Request operation. A one word input buffer then transmits the Status Reply to the computer. If an input or output operation is to follow, the computer program places the terminal address plus one in the appropriate control address. An Activate instruction follows and buffering proceeds in the normal manner except only the lower 12 bits of data are transmitted to or from computer storage.

The EXF 7 instructions sense the condition of an external equipment or the internal conditions (faults) of the computer. If the specified condition exists, a skip exit is performed; if not present, an exit is performed (Example 1).

| Example 1 | (00110) | 74 | 7 | 00011 |

|-----------|---------|----|---|-------|

|           | (00111) | 75 | 0 | 00007 |

|           | (00112) | 53 | 1 | 00005 |

In this example, the translation of program step 00110 is skip on channel 1 inactive. If channel 1 is inactive the next instruction to be executed would be program step 00112, i.e., 53 1 00005. If channel 1 were active however, program step 00111 would be the next instruction executed. In either case, the sensing of a condition in no way alters the condition.

The EXF j instructions activate buffer channel j where j equals 1-6. The execution address of the instruction, y, must designate the starting address of the buffer region

in storage. These instructions are the only instructions which can initiate a buffer (information flow) between the computer and an external equipment.

The following steps should be completed prior to initiating a buffer operation.

- 1) Sense for: (a) channel inactive and (b) equipment ready.

- 2) Select the external equipment and its mode of operation.

- 3) Substitute the terminal address into the buffer control word.

An equipment is <u>ready</u> if there is no motion, that is, a transmission is not taking place.